立即下载

没有对应的手机版,本软件为电脑版,电脑版软件不支持手机安装

Cadence Allegro 17.2是一款非常强大的PCBs编辑器,也是目前该软件的最新版本。它提供全套编辑和布线设计。该应用程序帮助所有电气工程师和布局设计人员生产印刷电路板,从而为他们提供最先进的工具集,包括强大的编辑和布线功能。全新Cadence Allegro 17.2中的采用了新的数据存储方式,这也使其不再兼容以往的版本,即其设计的文件不能降级,同时还带来了新的padstack创建方式,但无论是在性能方面还是功能方面都可以说是得到了质的飞跃。Cadence Allegro的核心是自动布线电路,能够正确连接电路板上的组件,并且不会影响您的设计。软件还可以处理高度复杂的项目,缩短设计周期,同时检查完整性。嵌入式3D查看器允许您在将设计发送到制造部门并提供深度观察所需的所有可视化工具之前,对其进行分析和研究。

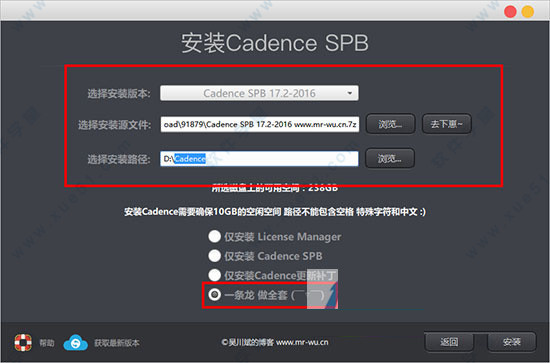

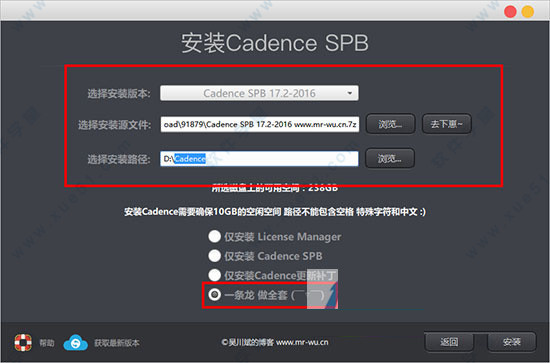

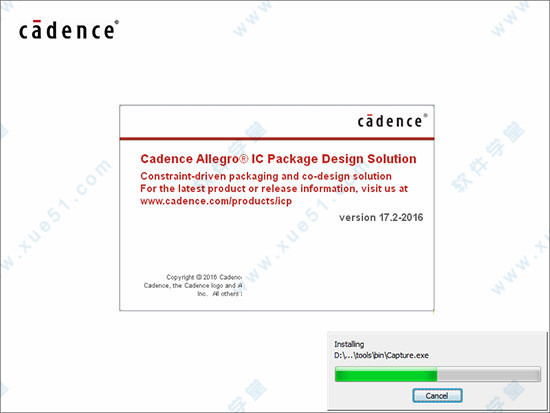

2、安装包直接解压需要密码并且会解压错误,我们直接运行破戒大师,选择第一项“安装Cadence SPB软件”,然后点击继续。

3、选择安装版本为Cadence SPB 17.2-2016,选择安装源文件为7Z压缩包,选择安装路径为英文路径,然后点击“一条龙 做全套”安装。

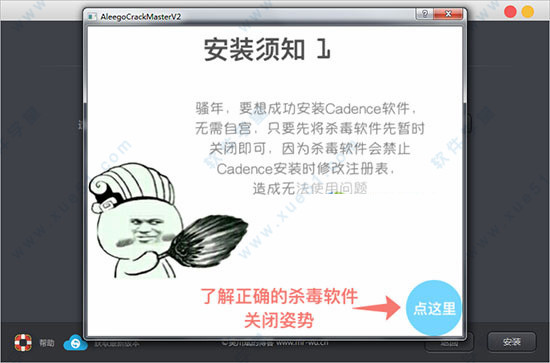

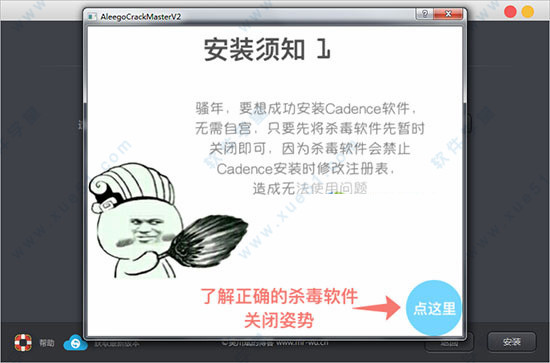

4、注意在安装软件的时候,请先关闭杀毒软件。

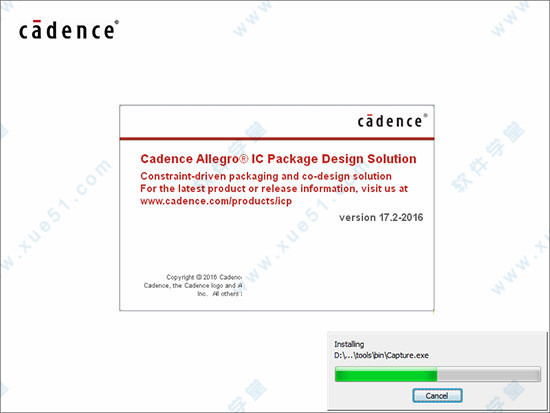

5、安装过程中不要随意点击鼠标,耐心等待安装完成即可。

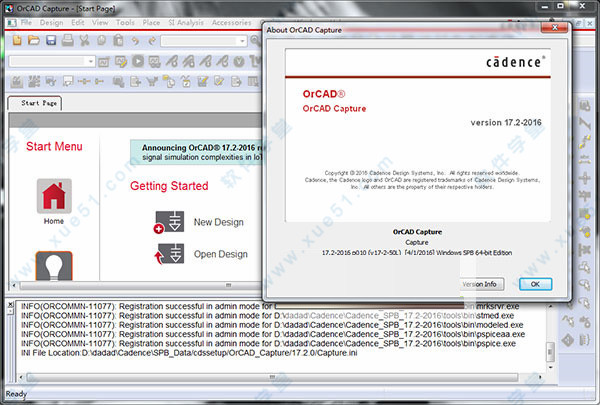

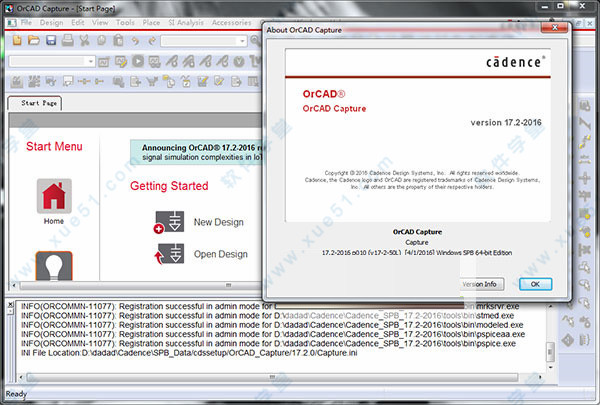

6、好了软件成功安装,现在无需多余的手动破解操作。

操作系统:Windows 7/8/8.1/10

内存(RAM):需要8 GB的RAM。

硬盘空间:需要6 GB的可用空间。

处理器:2.66 GHz Intel Core 2 Duo或更高版本。

1、文件版本不可以降级

即Cadence 17.2-2016 可以打开16.x版本的设计文件,但是Cadence 17.2-2016保存的文件无法再降级到16.x版本下,因此建议务必做备份。

2、Cadence Download Manager

使用CadenceDownload Manager可以自动获取软件更新,并可以进行自动下载、安装;用户还可以通过该工具自定义更新计划;

3、Cadence OrCAD、Allegro 产品的相关程序的安装目录结构变更:

Cadence OrCAD、Allegro 17.2-2016 的相关应用程序安装路径调整至安装路径中的/tools/bin下。因此环境变量PATH中将可不需定义 pcb/bin 及 fet/bin 的路径。而执行

Cadence OrCAD、Allegro 17.2-2016 相关应用程序亦可不需设定 17.2-2016 的相关路径于环境变量中。

Cadence SPB Switch Release 17.2-2016 版本切换工具已更新,其可辨别不同版本间的应用程序路径,用以自动更新应用程序与档案连结性关系。

若您使用cmd控制台或批处理程序(batch file),请将您原批处理程序加入 17.2-2016 安装路径中的/tools/bin 文件夹路 径下的 allegro_cmd.bat。

OrCAD Products 支援 TCL 8.6 64 位版本

4、开始菜单

安装好软件之后,在 Windows 的开始菜单里,Cadence 产品根据不同类别进行了调整,更方便管理和查找启动。老wu试了一下,貌似在win7分组功能可以,但是win10下分组无效,反而更糟糕。

二、OrCAD Capture 17.2-2016的新功能

1、设计差异比对

当两份电路图有所差异时,透过 Capture Compare Design 功能可以选择对电路图资料夹或是电路图图纸页面做差异比对,比对结果可查看电路图逻辑或是图形的差异。

在 Capture 命列选单中,选择 Tools >> Compare Designs 功能选单来进行电路图的差异比对。

2、高级零件标号编排功能(Advanced Annotation)

在Capture 中新增了高级零件标号编排的功能,在这个功能中,你可以针对不同电路图图纸页面设定不同的零件序号起始值,同时也可以针对同一页电路图图纸不同零件设定不同的起始序号。

3、新增个人工作环境设定

OrCAD Capture现在对使用者环境设定,有更加高级的设定界面,使用功能选单中的 Option >> Preference >> More Preference 进入设定界面。在新的 Extended Preferences Setup 中,可以针对以下环境做高级设定:

命令窗口(Command Shell)

设计及零件库(Design and Libraries)

设计缓存(Design Cache)

设计规则检查(DRC)

OrCAD Capture CIS (CIS)

网络群组(NetGroup)

网表(NetList)

电路图(Schematic)

4、范例设计浏览

在 Cadence 17.2-2016软件安装目录中,整合并提供了 150 个以上的范例档案让使用者可以快速了解及学习 OrCAD Capture、OrCAD Capture CIS 以及 OrCAD Capture–OrCAD PSpice 设计流程的设计。在 OrCAD Capture 17.2-2016 中,可以简单地透过 File – Open – Demo Design 的功能选单开启内建范例档案。

5、档案格式的输出与输入

OrCAD Capture 使用File –> Export –> Design XML 或 Library XML 指令以及File –> Import –> Design XML 或Library XML 指令,可以透过<程式安装目录中>toolscapturetclscriptscapdbdsn.xd、olb.xd 程式将电路图、零件库输出为XML 格式,以及将XML 格式重新载入成为标准电路图、零件库。

6、Intel Schematic Export Format (ISCF)格式输出

OrCAD Capture 可以使用 File –> Export –> ISCF 介面针对电路图零件、管脚属性与接地信号输出 Intel Schematic Export Format (ISCF) 格式。此格式可以通过用户界面设定零件或零件管脚属性的输出,输出后这些设定将被存档于 Caputre.ini 档案中以便下次使用不需重新设定。

7、PDF输出

从OrCAD Capture 17.2-2016 版本后,若你的电脑有安装ghostscript 32 bit、ghostscript 64 bit、 Adobe Acrobat Distiller…等程序,可以使用File –> Export –> PDF 的功能命令将电路图直接导出为PDF文档。导出内容包含:

OrCAD Capture 设计

显示设计层级架构

显示零件序号列表

显示网络及与其连接的零件脚位

可跳转至层级式方块内的设计

点选元件可显示元件属性

导览显示 off-page connector 的连结

8、OrCAD Capture 设计元件

此元件属性 PDF 文档支持与 OrCAD Capture PDF 文档的 cross-probing 功能。

9、新增 OrCAD PSpice 仿真模型于 Capture –> PSpice 设计流程

OrCAD Capture 对于 Capture -> PSpice 设计流程,新增 OrCAD PSpice 仿真模型,如下表。

10、其他项目的新增功能

针对电路图 Intersheet Reference 功能,增加对 X 轴向可偏移的设定,可设定负数值做偏移位置设定。

三、OrCAD Capture CIS 17.2-2016 新功能

1、水晶报表 (Crystal Report)

OrCAD Capture CIS 17.2-2016 版本预设针对 ODBC 连接数据库与水晶报表(Crystal Report)的连接方式改为使用 SQLite 连接到数据库中。

连接信息如下:

DRIVER=SQLite3 ODBC Driver;Database=”SQLite DB file Name”;LongNames = 0;Timeout = 1000; NoTXN = 0;SyncPragma=NORMAL;StepAPI=0;NoWCHAR=1;

四、OrCad PSpice 17.2-2016 新功能

1、PSpice DMI (Device Modeling Interface)Template Code 产生器

于 PSpice 17.2-2016 可使用 PSpice 模型编辑器(Model Editor)的 DMI (Device Modeling Interface)Template Code 产生器产出 PSpice 连接码(Adaptor code)。 PSpice 连接码启动 PSpice 仿真时使用 PSpice DMI DLL 文档。将模拟/数字的 C/C++及 SystemC 模型(Model)的模型码(Model Code)加入 PSpice 连接码中并使用 Microsoft Visual Studio Express 2013 建立 PSpice DMI DLL 库。当 Spice DMI DLL 库产生后,将其对应的 PSpice 模型(.lib)使用 PSpice 模型编辑器快速建立 OrCAD Capture 元件,便可运用此 PSpice 模型于 PSpice 设计仿真流程中。PSpice DMI Template Code 产生器提供以下元件类型:

●模拟基础元件:

通用零件(Generic device)

电压控制电压源(Voltage-Controlled Voltage Source)

相依电压源(Function-Dependent Voltage Source)

电压控制电流源(Voltage-Controlled Current Source)

相依电流源(Function-Dependent Current Source)

两端点零件(Generic Two-Node Device)

三端点零件(Generic Three-Node Device)

数字 C/C++基础零件

SystemC 基础零件

Verilog-A 基础零件

2、新增行为仿真模型的延迟(Delay)功能

DelayT()及 DelayT1()功能简化传统上使用的延迟功能,例如,TLINE 及 Laplace 函数,其减少在收敛上的问题,并比传统功能信号(电压或电流)有更快的计算。

–DelayT() 功能的语法为 delayt(v(x),, ) 例:E2 out 0 value {delayt(V(x),5m, 10m)}

–DelayT1()功能的语法为 delayt1(v(x),) 例:E2 out 0 value {delayt1(V(x),5m)}

3、OPTIONS 指令的 Flag 选项新增 SKIPTOPO

当 Flag 选项设定 SKIP TOPO = 1 时,则 OrCAD Capture 将跳过拓扑检查(topology checks)。

例:.options SKIPTOPO = 1

支持使用负值于迟滞电压(Hysteresis voltage)及临界电压(threshold voltage)中

五、OrCAD PCB Designer 17.2-2016 新功能

1、全新 Padstack 编辑器界面

新的 Padstack Editor 界面,简化了设定各种不同 Padstack 的不必要的步骤,使用者只需要在 Start 页面选择要建立的种类与几何形状之后,就能在其他页面进行相关细节的设定。

2、动态铜支持分层定义

对于动态铜的 Pin/Via 连接及隔离设定,在新的版本中能够分层来做特别的定义。

3、以下的设置也支持分层设定:

Dyn_clearance_oversize_array

Dyn_clearance_type

Dyn_fixed_therm_width_array

Dyn_max_thermal_conns

Dyn_min_thermal_conns

Dyn_oversize_therm_width_array

Dyn_thermal_best_fit

Dyn_thermal_con_type

4、全新的层叠结构界面

重新设计的叠构编辑设定,充分运用表格式的方法来进行相关设定,其创意来自于 Constraint Manager 的格式,藉由一致性的表格来让使用者操作上更为易用。

新的界面整合了 Unused Pad Suppression 与 Embedded Component 设定还有支持了非电气层的部 ,如:Solder mask, Paste, Coverlay…等;另外对于 Material 的字符长度也扩展到 250 个字符。

5、支持软硬结合板的多重叠构设计

对应多重叠构的软硬结合板设计,可透过 Cross Section Editor 设定。

6、软硬板的区域范围管理

新增实体区域来分别定义软板或硬板的区域范围。

新增 Classes 及 Subclass 类型

加入软硬结合板及表面处理的 Class。

7、新增 Design Outline 及CUTOUTS subclasses

对于 Board Geometry 新加入了Design Outline及CUTOUTS的subclass供日后更宽广的应用。

8、动态区域摆放

对于不同叠构层面的软硬结合板,在摆放零件时能够依照所属的区域将零件摆放到正确的层面上

9、新增动态网状铜

动态铜现在能直接铺设网状铜。

10、软件结合板的Inter Layer Checks

软硬结合板设计因分别拥有不同的mask 及表面涂层,并且对于软板部分还会有弯折的区域,所以要能够确实做到相对的检查以避免设计因生产组装时发生错误,就能透过Inter Layer Checks 设定相关检查条件。

弯折区域对于 Pin, Via 的检查

覆盖范围检查

软硬结合板的生产资料

Cross section chart支持多重叠构的表格

11、动态泪滴铺铜设置

动态补泪滴补铜现在可对各层面进行设定。

12、新增缺少的 Tapered trace 执行输出报告

新增的报表,可将缺少的渐变 Tapered trace 输出报表

13、多元的编辑指令模式

v16.6-2015时新增可快速对 Shape 编辑的操作模式,在v17.2延续良好的操作编辑特性,再加入了更多元的编辑指令。

14、全新的 Color Dialog

资料的呈现是很重要的一环,因此新的 Color dialog 将会让您以更快速更有效率的方式来操作使用。

15、新的视觉呈现

新的界面以标签页方式来呈现 Layers / Nets / Display / Favorites / Visibility Pane。

能透过 Filter 快速筛选出想设定的元件出来。

可以控制显示物件种类,以及在多重叠构下各叠构显示的层面设定

六、用户界面的更新

1、可自定义的工具栏

提供更能够个人化的自定义工具栏属性,现在能让更多指令变成一个图标。

2、状态栏的显示与隐藏设定

现在您可以设定 Status bar 上需要显示或隐藏的信息。

3、锐角检测

对于锐角的检查,使用者可以通过定义锐角角度来将以下四种情况进行确认。

Line to Pad

Line to Shape

Shape Edge to Edge

Line to Line

4、孔的间距检查

通过 Check holes within pads 的设定,无论 Hole 有无 Pad 皆会依 CM Spacing 内 Hole 的间距设定执行检查。

5、维持 Padstacks 定义

如果设计当中有对零件包装进行 Replace Padstack,那么在 Refresh Symbol 时能够选择是否要保留 现在设计中的 Padstack 名称而不被刷新。

6、效能提升

CPU 效能提升 10-20%。

Import logic 对于有很多 Pin 数的 Device(>2k pins)条件时,处理速度比以往都要快。

7、字符长度增加

Default internal 的名称长度由原本的 32 个字符现可增加到 255 个字符。

安装破解教程

1、首先在本站下载好安装包和阿狸狗破戒大师。2、安装包直接解压需要密码并且会解压错误,我们直接运行破戒大师,选择第一项“安装Cadence SPB软件”,然后点击继续。

3、选择安装版本为Cadence SPB 17.2-2016,选择安装源文件为7Z压缩包,选择安装路径为英文路径,然后点击“一条龙 做全套”安装。

4、注意在安装软件的时候,请先关闭杀毒软件。

5、安装过程中不要随意点击鼠标,耐心等待安装完成即可。

6、好了软件成功安装,现在无需多余的手动破解操作。

系统需求

【最低配置】操作系统:Windows 7/8/8.1/10

内存(RAM):需要8 GB的RAM。

硬盘空间:需要6 GB的可用空间。

处理器:2.66 GHz Intel Core 2 Duo或更高版本。

全新功能

一、Cadence SPB 17.2-2016升级所带来的新功能介绍如下:1、文件版本不可以降级

即Cadence 17.2-2016 可以打开16.x版本的设计文件,但是Cadence 17.2-2016保存的文件无法再降级到16.x版本下,因此建议务必做备份。

2、Cadence Download Manager

使用CadenceDownload Manager可以自动获取软件更新,并可以进行自动下载、安装;用户还可以通过该工具自定义更新计划;

3、Cadence OrCAD、Allegro 产品的相关程序的安装目录结构变更:

Cadence OrCAD、Allegro 17.2-2016 的相关应用程序安装路径调整至安装路径中的/tools/bin下。因此环境变量PATH中将可不需定义 pcb/bin 及 fet/bin 的路径。而执行

Cadence OrCAD、Allegro 17.2-2016 相关应用程序亦可不需设定 17.2-2016 的相关路径于环境变量中。

Cadence SPB Switch Release 17.2-2016 版本切换工具已更新,其可辨别不同版本间的应用程序路径,用以自动更新应用程序与档案连结性关系。

若您使用cmd控制台或批处理程序(batch file),请将您原批处理程序加入 17.2-2016 安装路径中的/tools/bin 文件夹路 径下的 allegro_cmd.bat。

OrCAD Products 支援 TCL 8.6 64 位版本

4、开始菜单

安装好软件之后,在 Windows 的开始菜单里,Cadence 产品根据不同类别进行了调整,更方便管理和查找启动。老wu试了一下,貌似在win7分组功能可以,但是win10下分组无效,反而更糟糕。

二、OrCAD Capture 17.2-2016的新功能

1、设计差异比对

当两份电路图有所差异时,透过 Capture Compare Design 功能可以选择对电路图资料夹或是电路图图纸页面做差异比对,比对结果可查看电路图逻辑或是图形的差异。

在 Capture 命列选单中,选择 Tools >> Compare Designs 功能选单来进行电路图的差异比对。

2、高级零件标号编排功能(Advanced Annotation)

在Capture 中新增了高级零件标号编排的功能,在这个功能中,你可以针对不同电路图图纸页面设定不同的零件序号起始值,同时也可以针对同一页电路图图纸不同零件设定不同的起始序号。

3、新增个人工作环境设定

OrCAD Capture现在对使用者环境设定,有更加高级的设定界面,使用功能选单中的 Option >> Preference >> More Preference 进入设定界面。在新的 Extended Preferences Setup 中,可以针对以下环境做高级设定:

命令窗口(Command Shell)

设计及零件库(Design and Libraries)

设计缓存(Design Cache)

设计规则检查(DRC)

OrCAD Capture CIS (CIS)

网络群组(NetGroup)

网表(NetList)

电路图(Schematic)

4、范例设计浏览

在 Cadence 17.2-2016软件安装目录中,整合并提供了 150 个以上的范例档案让使用者可以快速了解及学习 OrCAD Capture、OrCAD Capture CIS 以及 OrCAD Capture–OrCAD PSpice 设计流程的设计。在 OrCAD Capture 17.2-2016 中,可以简单地透过 File – Open – Demo Design 的功能选单开启内建范例档案。

5、档案格式的输出与输入

OrCAD Capture 使用File –> Export –> Design XML 或 Library XML 指令以及File –> Import –> Design XML 或Library XML 指令,可以透过<程式安装目录中>toolscapturetclscriptscapdbdsn.xd、olb.xd 程式将电路图、零件库输出为XML 格式,以及将XML 格式重新载入成为标准电路图、零件库。

6、Intel Schematic Export Format (ISCF)格式输出

OrCAD Capture 可以使用 File –> Export –> ISCF 介面针对电路图零件、管脚属性与接地信号输出 Intel Schematic Export Format (ISCF) 格式。此格式可以通过用户界面设定零件或零件管脚属性的输出,输出后这些设定将被存档于 Caputre.ini 档案中以便下次使用不需重新设定。

7、PDF输出

从OrCAD Capture 17.2-2016 版本后,若你的电脑有安装ghostscript 32 bit、ghostscript 64 bit、 Adobe Acrobat Distiller…等程序,可以使用File –> Export –> PDF 的功能命令将电路图直接导出为PDF文档。导出内容包含:

OrCAD Capture 设计

显示设计层级架构

显示零件序号列表

显示网络及与其连接的零件脚位

可跳转至层级式方块内的设计

点选元件可显示元件属性

导览显示 off-page connector 的连结

8、OrCAD Capture 设计元件

此元件属性 PDF 文档支持与 OrCAD Capture PDF 文档的 cross-probing 功能。

9、新增 OrCAD PSpice 仿真模型于 Capture –> PSpice 设计流程

OrCAD Capture 对于 Capture -> PSpice 设计流程,新增 OrCAD PSpice 仿真模型,如下表。

10、其他项目的新增功能

针对电路图 Intersheet Reference 功能,增加对 X 轴向可偏移的设定,可设定负数值做偏移位置设定。

三、OrCAD Capture CIS 17.2-2016 新功能

1、水晶报表 (Crystal Report)

OrCAD Capture CIS 17.2-2016 版本预设针对 ODBC 连接数据库与水晶报表(Crystal Report)的连接方式改为使用 SQLite 连接到数据库中。

连接信息如下:

DRIVER=SQLite3 ODBC Driver;Database=”SQLite DB file Name”;LongNames = 0;Timeout = 1000; NoTXN = 0;SyncPragma=NORMAL;StepAPI=0;NoWCHAR=1;

四、OrCad PSpice 17.2-2016 新功能

1、PSpice DMI (Device Modeling Interface)Template Code 产生器

于 PSpice 17.2-2016 可使用 PSpice 模型编辑器(Model Editor)的 DMI (Device Modeling Interface)Template Code 产生器产出 PSpice 连接码(Adaptor code)。 PSpice 连接码启动 PSpice 仿真时使用 PSpice DMI DLL 文档。将模拟/数字的 C/C++及 SystemC 模型(Model)的模型码(Model Code)加入 PSpice 连接码中并使用 Microsoft Visual Studio Express 2013 建立 PSpice DMI DLL 库。当 Spice DMI DLL 库产生后,将其对应的 PSpice 模型(.lib)使用 PSpice 模型编辑器快速建立 OrCAD Capture 元件,便可运用此 PSpice 模型于 PSpice 设计仿真流程中。PSpice DMI Template Code 产生器提供以下元件类型:

●模拟基础元件:

通用零件(Generic device)

电压控制电压源(Voltage-Controlled Voltage Source)

相依电压源(Function-Dependent Voltage Source)

电压控制电流源(Voltage-Controlled Current Source)

相依电流源(Function-Dependent Current Source)

两端点零件(Generic Two-Node Device)

三端点零件(Generic Three-Node Device)

数字 C/C++基础零件

SystemC 基础零件

Verilog-A 基础零件

2、新增行为仿真模型的延迟(Delay)功能

DelayT()及 DelayT1()功能简化传统上使用的延迟功能,例如,TLINE 及 Laplace 函数,其减少在收敛上的问题,并比传统功能信号(电压或电流)有更快的计算。

–DelayT() 功能的语法为 delayt(v(x),, ) 例:E2 out 0 value {delayt(V(x),5m, 10m)}

–DelayT1()功能的语法为 delayt1(v(x),) 例:E2 out 0 value {delayt1(V(x),5m)}

3、OPTIONS 指令的 Flag 选项新增 SKIPTOPO

当 Flag 选项设定 SKIP TOPO = 1 时,则 OrCAD Capture 将跳过拓扑检查(topology checks)。

例:.options SKIPTOPO = 1

支持使用负值于迟滞电压(Hysteresis voltage)及临界电压(threshold voltage)中

五、OrCAD PCB Designer 17.2-2016 新功能

1、全新 Padstack 编辑器界面

新的 Padstack Editor 界面,简化了设定各种不同 Padstack 的不必要的步骤,使用者只需要在 Start 页面选择要建立的种类与几何形状之后,就能在其他页面进行相关细节的设定。

2、动态铜支持分层定义

对于动态铜的 Pin/Via 连接及隔离设定,在新的版本中能够分层来做特别的定义。

3、以下的设置也支持分层设定:

Dyn_clearance_oversize_array

Dyn_clearance_type

Dyn_fixed_therm_width_array

Dyn_max_thermal_conns

Dyn_min_thermal_conns

Dyn_oversize_therm_width_array

Dyn_thermal_best_fit

Dyn_thermal_con_type

4、全新的层叠结构界面

重新设计的叠构编辑设定,充分运用表格式的方法来进行相关设定,其创意来自于 Constraint Manager 的格式,藉由一致性的表格来让使用者操作上更为易用。

新的界面整合了 Unused Pad Suppression 与 Embedded Component 设定还有支持了非电气层的部 ,如:Solder mask, Paste, Coverlay…等;另外对于 Material 的字符长度也扩展到 250 个字符。

5、支持软硬结合板的多重叠构设计

对应多重叠构的软硬结合板设计,可透过 Cross Section Editor 设定。

6、软硬板的区域范围管理

新增实体区域来分别定义软板或硬板的区域范围。

新增 Classes 及 Subclass 类型

加入软硬结合板及表面处理的 Class。

7、新增 Design Outline 及CUTOUTS subclasses

对于 Board Geometry 新加入了Design Outline及CUTOUTS的subclass供日后更宽广的应用。

8、动态区域摆放

对于不同叠构层面的软硬结合板,在摆放零件时能够依照所属的区域将零件摆放到正确的层面上

9、新增动态网状铜

动态铜现在能直接铺设网状铜。

10、软件结合板的Inter Layer Checks

软硬结合板设计因分别拥有不同的mask 及表面涂层,并且对于软板部分还会有弯折的区域,所以要能够确实做到相对的检查以避免设计因生产组装时发生错误,就能透过Inter Layer Checks 设定相关检查条件。

弯折区域对于 Pin, Via 的检查

覆盖范围检查

软硬结合板的生产资料

Cross section chart支持多重叠构的表格

11、动态泪滴铺铜设置

动态补泪滴补铜现在可对各层面进行设定。

12、新增缺少的 Tapered trace 执行输出报告

新增的报表,可将缺少的渐变 Tapered trace 输出报表

13、多元的编辑指令模式

v16.6-2015时新增可快速对 Shape 编辑的操作模式,在v17.2延续良好的操作编辑特性,再加入了更多元的编辑指令。

14、全新的 Color Dialog

资料的呈现是很重要的一环,因此新的 Color dialog 将会让您以更快速更有效率的方式来操作使用。

15、新的视觉呈现

新的界面以标签页方式来呈现 Layers / Nets / Display / Favorites / Visibility Pane。

能透过 Filter 快速筛选出想设定的元件出来。

可以控制显示物件种类,以及在多重叠构下各叠构显示的层面设定

六、用户界面的更新

1、可自定义的工具栏

提供更能够个人化的自定义工具栏属性,现在能让更多指令变成一个图标。

2、状态栏的显示与隐藏设定

现在您可以设定 Status bar 上需要显示或隐藏的信息。

3、锐角检测

对于锐角的检查,使用者可以通过定义锐角角度来将以下四种情况进行确认。

Line to Pad

Line to Shape

Shape Edge to Edge

Line to Line

4、孔的间距检查

通过 Check holes within pads 的设定,无论 Hole 有无 Pad 皆会依 CM Spacing 内 Hole 的间距设定执行检查。

5、维持 Padstacks 定义

如果设计当中有对零件包装进行 Replace Padstack,那么在 Refresh Symbol 时能够选择是否要保留 现在设计中的 Padstack 名称而不被刷新。

6、效能提升

CPU 效能提升 10-20%。

Import logic 对于有很多 Pin 数的 Device(>2k pins)条件时,处理速度比以往都要快。

7、字符长度增加

Default internal 的名称长度由原本的 32 个字符现可增加到 255 个字符。

展开全部内容

点击星星用来评分